O salto para Zen 4 não está acontecendo este ano, mas a AMD já tem uma resposta para a Intel Lago de Amieiro plataforma. Como anunciado na Computex no início deste verão, a AMD irá atualizar seus processadores Zen 3 com o 3D V-Cache no início de 2022, e isto deve ser suficiente até mesmo para o campo de jogo contra a Intel, pelo menos até o lançamento da próxima geração, no final de 2022. No simpósio anual Hot Chips, a AMD recentemente forneceu mais detalhes sobre como funciona o V-Cache 3D e também ofereceu uma prévia para suas futuras aplicações de empilhamento 3D.

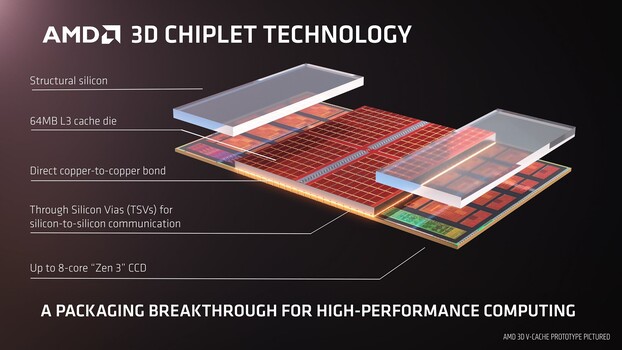

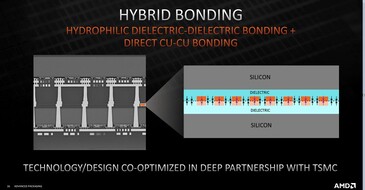

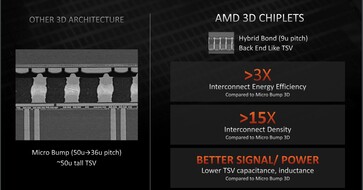

A AMD está implementando um pacote de 9 mícrons de chiplets Micro Bump 3D para o V-Cache através de silício via (TSV). Embora apenas 1 mícron mais fino que o da Intel Foveros 3D empilhamento que será usado para produzir os processadores do Lago Alder, diz-se que os Micro Bumps da AMD oferecem mais de 3 vezes a eficiência energética de interconexão, 15 vezes a densidade de interconexão e a capacitância/indutância. A atual tecnologia TSV que atua como uma conexão vertical entre pastilhas ou entre matrizes não oferece muitas ligações, mas, no futuro, o passo TSV se tornará cada vez mais refinado, permitindo projetos mais complexos de empilhamento 3D. O V-Cache, por exemplo, permite a comunicação completa entre silício e silício (DRAM na CPU / CPU na CPU) através de ligações diretas entre cobre e cobre. Isto permite a adição de 64 MB de cache L3 à quantidade existente, o que supostamente proporciona um aumento de desempenho de 15% em jogos e de 19% em aplicações de criação de conteúdo.

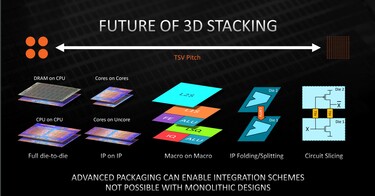

Os campos TSV mais finos permitirão técnicas complexas de empilhamento 3D, incluindo IP sobre IP (núcleos sobre núcleos / núcleos sobre uncore), macro sobre macro (SoCs em SoCs), e eventualmente até mesmo a dobra / divisão de IP e o corte de circuitos. Os requisitos de energia também diminuirão em mais de 3 vezes. Provavelmente veremos a primeira aplicação da técnica IP sobre IP com a Núcleos RDNA2 GPU empilhados em cima dos núcleos Zen 4

Leaked AMD documents confirm integrated GPUs for next-generation Socket AM5 processors

Os Top 10

» Os Top 10 Portáteis Multimídia

» Os Top 10 Portáteis de Jogos

» Os Top 10 Portáteis Leves para Jogos

» Os Top 10 Portáteis Acessíveis de Escritório/Empresariais

» Os Top 10 Portáteis Premium de Escritório/Empresariais

» Os Top 10 dos Portáteis Workstation

» Os Top 10 Subportáteis

» Os Top 10 Ultrabooks

» Os Top 10 Conversíveis

» Os Top 10 Tablets

» Os Top 10 Smartphones

» A melhores Telas de Portáteis Analisadas Pela Notebookcheck

» Top 10 dos portáteis abaixo dos 500 Euros da Notebookcheck

» Top 10 dos Portáteis abaixo dos 300 Euros