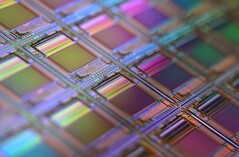

E se o seu disco rígido pudesse pensar com seus dados? Em vez de apenas armazenar arquivos, imagine-o processando e respondendo às informações exatamente onde elas são mantidas. Esse é o princípio por trás da computação na memória - uma mudança crescente na arquitetura que aproxima a lógica da memória para aumentar a eficiência.

Agora, os pesquisadores do Forschungszentrum Jülich e da Universidade de Duisburg-Essen apresentaram um novo design baseado em memristor 2T1R que poderia suportar essa mudança, permitindo uma IA mais eficiente em termos de energia e hardware de ponta.

Publicado em arXivo projeto integra dois transistores e um memristor por célula, com regulação de corrente destinada a suprimir correntes de caminho furtivo, um desafio conhecido em matrizes de memristor. Diferentemente da memória convencional, o projeto proposto aterra ambos os terminais do memristor quando ociosos - uma estratégia que pode ajudar a melhorar a estabilidade do sinal e reduzir o vazamento.

A arquitetura foi projetada para suportar a multiplicação analógica de matriz vetorial (VMM), uma função essencial no aprendizado de máquina, controlando a condutância do memristor usando DACs integrados, sinais PWM e caminhos de corrente regulados. Uma matriz de teste 2×2 foi implementada com sucesso usando a tecnologia CMOS padrão de 28 nm.

Ao abordar questões de aterramento virtual e efeitos de resistência de fio, a arquitetura visa melhorar a previsibilidade do desempenho e reduzir o consumo de energia. Com compatibilidade para controle RISC-V e interface digital, o design 2T1R pode estabelecer as bases para chips neuromórficos escaláveis, permitindo uma aceleração de IA mais rápida e compacta diretamente na memória.

Embora o seu disco rígido ainda não esteja pensando, a arquitetura por trás dessa visão já está tomando forma em silício, o que sugere um futuro de IA mais rápida e integrada à memória.

Para obter todos os detalhes técnicos e resultados, consulte o full arXiv preprint (PDF).

Fonte(s)

Os Top 10

» Os Top 10 Portáteis Multimídia

» Os Top 10 Portáteis de Jogos

» Os Top 10 Portáteis Leves para Jogos

» Os Top 10 Portáteis Acessíveis de Escritório/Empresariais

» Os Top 10 Portáteis Premium de Escritório/Empresariais

» Os Top 10 dos Portáteis Workstation

» Os Top 10 Subportáteis

» Os Top 10 Ultrabooks

» Os Top 10 Conversíveis

» Os Top 10 Tablets

» Os Top 10 Smartphones

» A melhores Telas de Portáteis Analisadas Pela Notebookcheck

» Top 10 dos portáteis abaixo dos 500 Euros da Notebookcheck

» Top 10 dos Portáteis abaixo dos 300 Euros